# **GPU COMPUTING**

Part 1

Ana Lucia Varbanescu (UvA)

## **HPC** computing

- Big Data, Big Simulation, Big Science

- Challenges

- Compute and storage

- Efficiency

- Performance vs. Energy

- HPC focuses traditionally on performance, but now moving towards efficiency

- Traditional HPC: complex machines, on-demand

- Modern HPC: more and more based on existing machines, put together in dense clusters/datacenters

- HPC is expanding to new application domains.

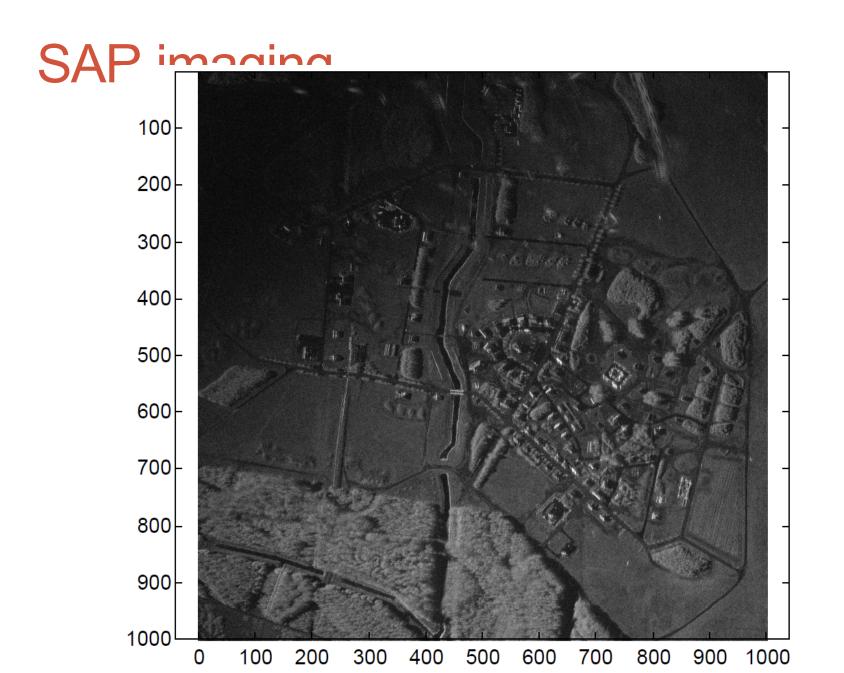

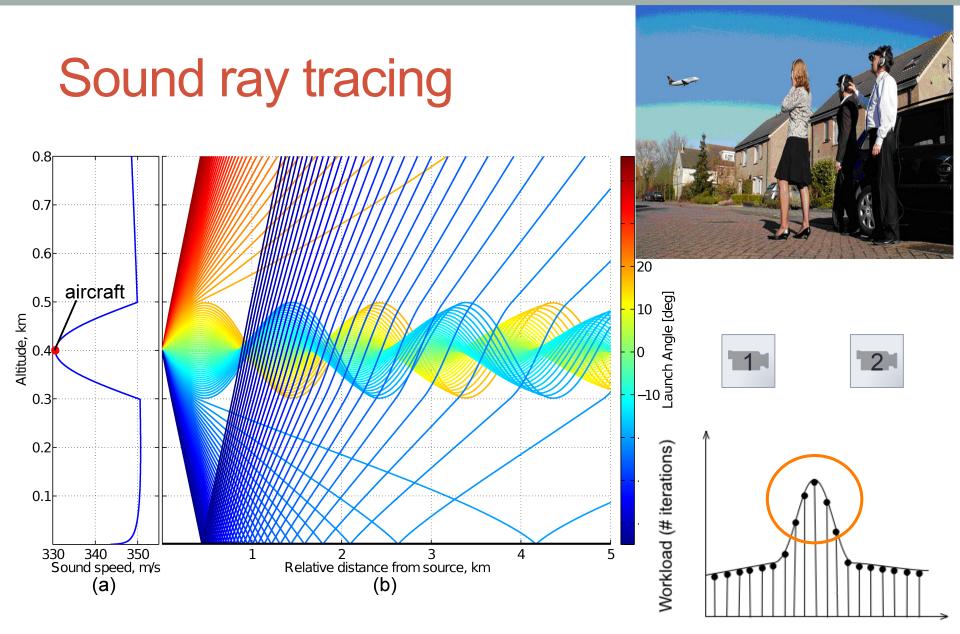

## Sound ray tracing

- A collaboration with Dutch NLR

- Simulate the sound propagation

- from an aircraft to receivers

Assess aircraft flyover noise during the aircraft take-off and approach procedures

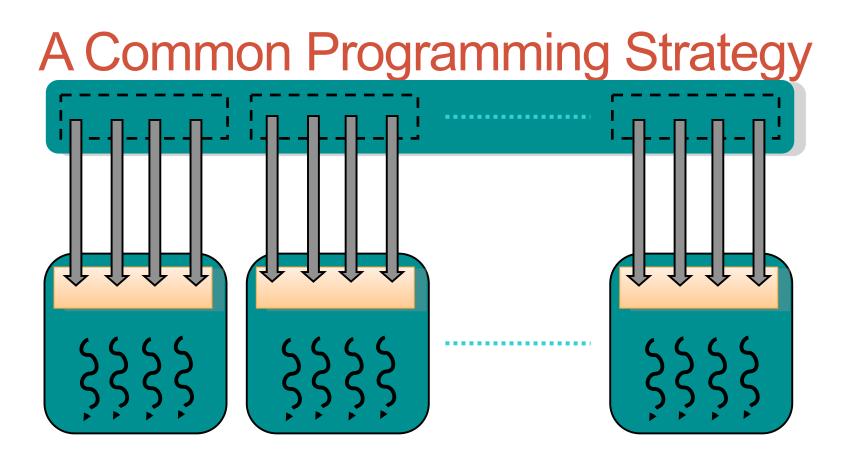

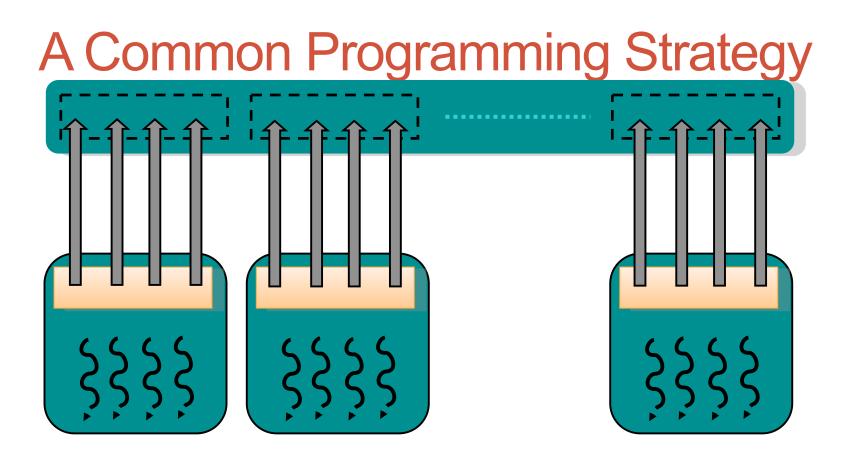

Ray ID (parallelization dimension)

# **BRIEFLY ON HARDWARE**

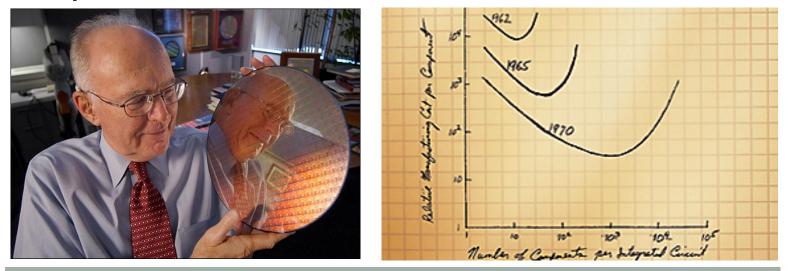

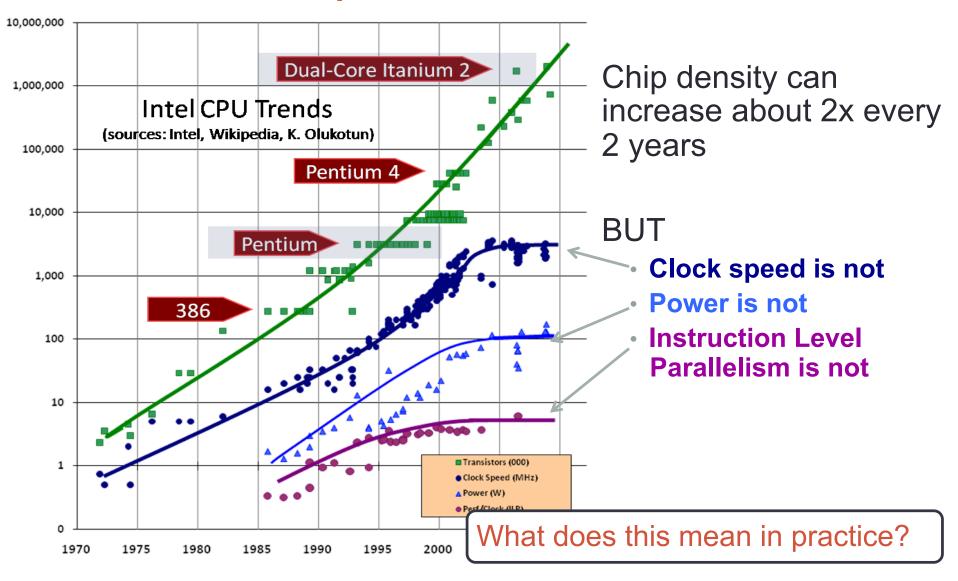

## Moore's Law

Gordon Moore (co-founder of Intel) predicted in 1965 that the transistor density of semiconductor chips would double roughly every 18 months.

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase...." Electronics Magazine 1965

### **Evolution of processors**

### New ways to use transistors

# **Improve PERFORMANCE by using parallelism on-chip**: multi-core (CPUs) and many-core processors (GPUs).

### Parallelism $\Leftrightarrow$ HPC

- Parallelism is mandatory for high performance

- Yesterday: clusters (and grids)

- Today: multi-/many-core processors

- Tomorrow: massive multi-scale heterogeneous parallelism = clusters using different types of multi-/many-cores

- >95% of computing systems today are parallel!

### Main challenges: learn to program parallel machines and learn to use them efficiently!

## Why talk about GPUs?

- GPUs are a steady market

- Gaming

- CAD-like activities

- Traditional or not ...

- Visualisation

- Scientific or not ...

GPUs are increasingly used for other types of applications

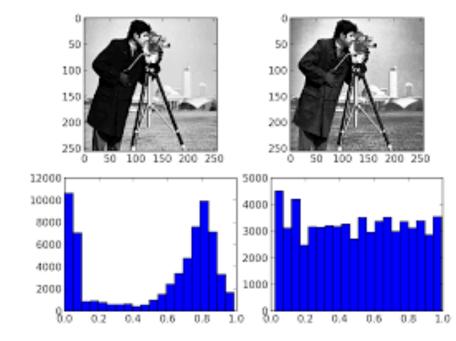

- Number crunching in science, finance, image processing

- (fast) Memory operations in big data processing

# GPGPU ?!

#### Massive parallelism => massive performance

### Graphics in 2015

### **GPUs in movies**

#### From Ariel in Little Mermaid to Brave

# Why GPUs?

- Promise of performance beyond most other architectures

- CPUs

- Multi-core CPUs

- FPGAs

- ...

- They are power efficient

- 2-5x better than a CPU

- What took us so long?

- These things are not easy to program ...

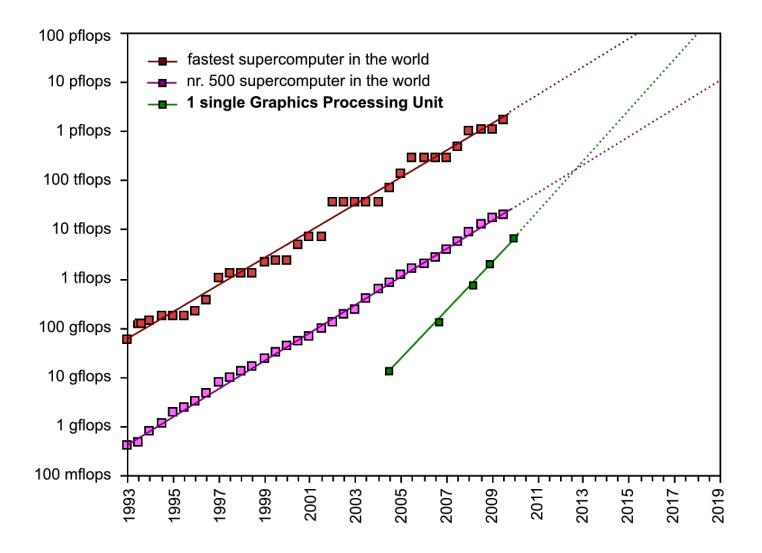

### **GPUs vs. supercomputers**

## **TODO List**

- 1. Introduction

- 2. GPGPUs & hardware performance

- 3. CUDA & application performance

- 4. Advanced CUDA

# **INTRODUCTION TO GPUS**

GPU = the processor GPGPU = general purpose computing on GPUs (typically refers to non-graphics stuff)

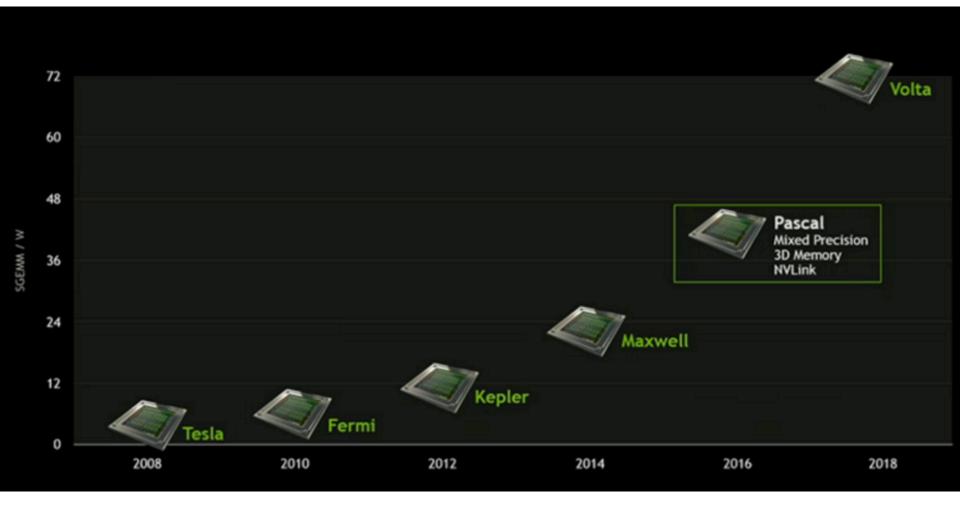

## GPUs @ NVIDIA

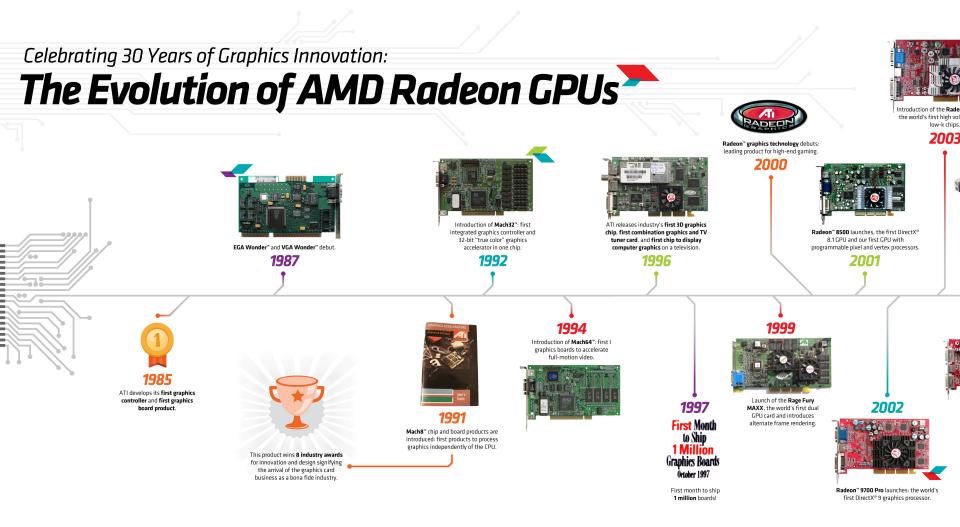

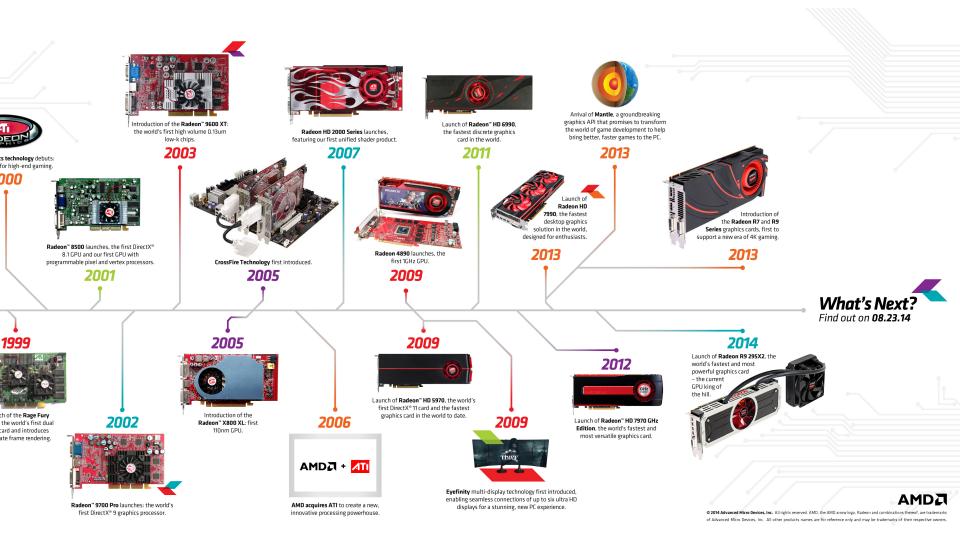

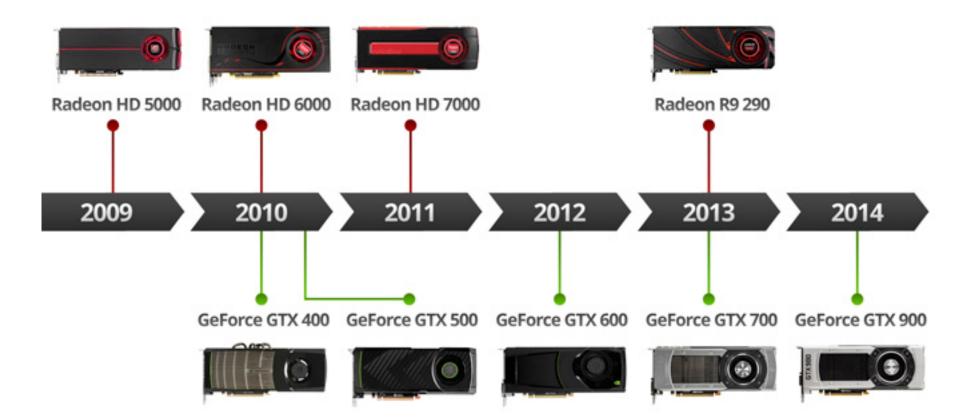

## GPUs @ ATI/AMD

21

## GPUs @ ATI/AMD

## **NVIDIA vs AMD**

### **NVIDIA vs AMD**

#### **AMD Radeon Graphics Roadmap**

### Radeon HD 7950

### Gpu

Clock speed Shading units Pixel rate Floating-point performance

# 320\$

1.050 MHz

58.8 GPixel/s

3,494 GFLOPS

1.664

### **GeForce GTX 970**

### Gpu

Clock speed Shading units Pixel rate Floating-point performance 800 MHz 1,792 25.6 GPixel/s 2,867 GFLOPS

311 \$

# As you can see nvidia is great choise under 311\$

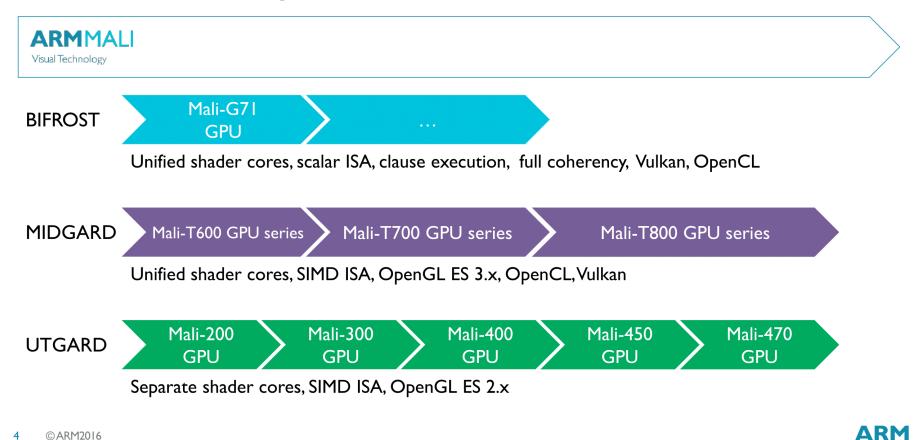

## GPUs @ ARM

### **ARM Mali Graphics Processor Generations**

EMBARGOED UNTIL 11pm EDT on Sunday, May 29

# **ON PERFORMANCE**

# Performance [1]

- Latency/delay

- The time for one operation (instruction) to finish, L

- To improve: minimize L

- Lower is better

- Throughput

- The number of operations (instructions) per time unit, T

- To improve: maximize T

- Higher is better

- Thus, time per instruction decreases, on average

- Example: 1 man builds a house in 10 days.

- Latency improvement: …

- Throughput improvement: ...

# Performance [2]

- How do we get faster computers?

- Faster processors and memory

- Increase clock frequency  $\rightarrow$  latency boost

- Better memory techniques

- Use memory hierarchies → latency boost

- More memory closer to processor → latency boost

- Better processing techniques

- Use pipelining  $\rightarrow$  throughput boost

- More processing units (cores, threads, ...)

- Use parallelism/concurrency → throughput boost (only?)

- Accelerators

- Use specialized functional units → latency+throughput boost

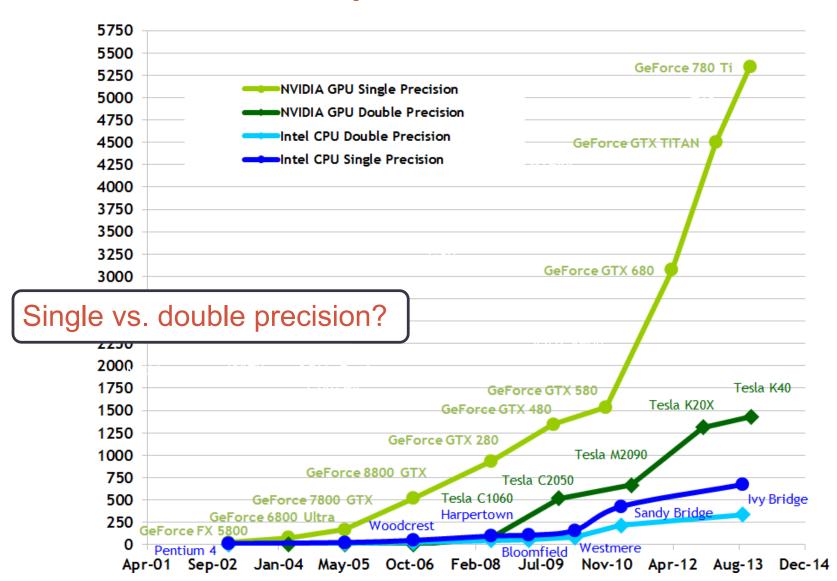

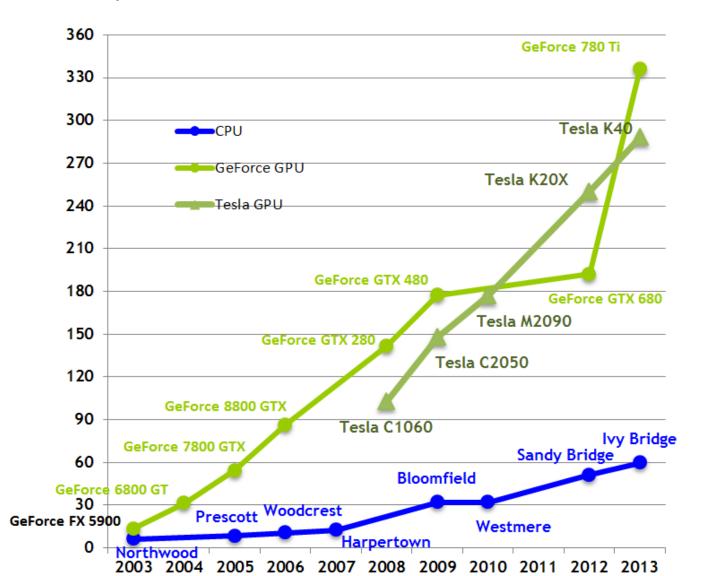

## Hardware Performance metrics

- Clock frequency [GHz] = absolute hardware speed

- Memories, CPUs, interconnects

#### Operational speed [GFLOPs]

- Operations per second

- single AND double precision

#### Memory bandwidth [GB/s]

- Memory operations per second

- Can differ for read and write operations !

- Differs a lot between different memories on chip

- Power [Watt]

- The rate of consumption of energy

- Derived metrics

- FLOP/Byte, FLOP/Watt

### Theoretical peak performance

Peak = chips \* cores \* vectorWidth \* FLOPs/cycle \* clockFrequency

- Examples

- Intel Core i7 CPU

- 2 chips \* 4 cores \* 4-way vectors \* 2 FLOPs/cycle \* 2.4 GHz = **154 GFLOPs**

- NVIDIA GTX 580 GPU

1 chip \* 16 SMs \* 32 cores \* 2 FLOPs/cycle \* 1.544 GhZ = **1581 GFLOPs**

• AMD HD 6970

1 chip \* 24 SIMD engines \* 16 cores \* 4-way vectors \* 2 FLOPs/cycle \* 0.880 GhZ = **2703 GFLOPs**

### GPULLA VIS CPU performance

### Main Memory bandwidth

Throughput = memory bus frequency \* bits per cycle \* bus width

- Memory clock != CPU clock

- In bits, divide by 8 for GB/s

- Examples:

- Intel Core i7 DDR3: 1.333 \* 2 \* 64 = **21 GB/s**

- NVIDIA GTX 580 GDDR5: 1.002 \* 4 \* 384 = **192 GB/s**

- ATI HD 6970 GDDR5:

1.375 \* 4 \* 256 = **176 GB/s**

### Memory bandwidths

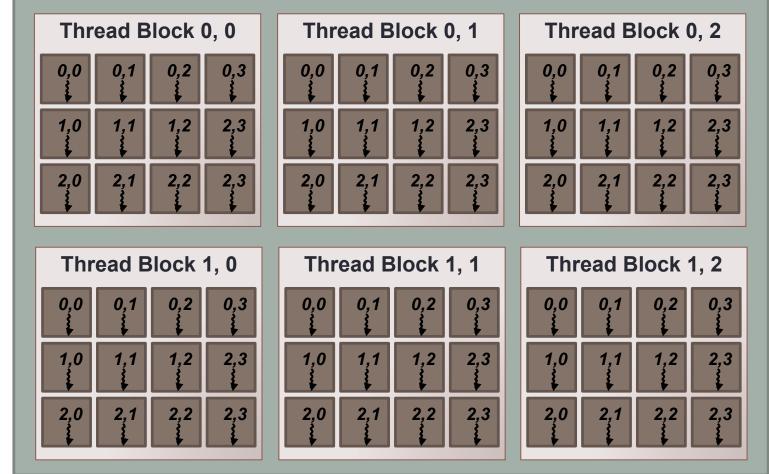

- On-chip memory can be orders of magnitude faster

- Registers, shared memory, caches, ...

- E.g., AMD HD 7970 L1 cache achieves 2 TB/s (vs. 176GB/s for main memory)

- Other memories: depends on the interconnect

- Intel's technology: QPI (Quick Path Interconnect)

- 25.6 GB/s

- AMD's technology: HT3 (Hyper Transport 3)

- 19.2 GB/s

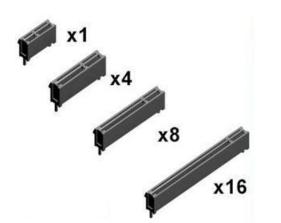

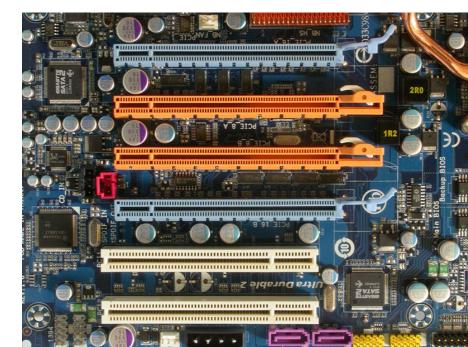

- Accelerators: PCI-e 2.0

- 8 GB/s

# GPU vs. CPU performance

### Power

- Chip manufactures specify Thermal Design Power (TDP)

- We can measure dissipated power

- Whole system

- Typically (much) lower than TDP

- Power efficiency

- FLOPS / Watt

- Examples (with theoretical peak and TDP)

- Intel Core i7:

- NVIDIA GTX 580:

- ATI HD 6970:

- 154 / 160 = **1.0 GFLOPs/W**

- 1581 / 244 = 6.3 GFLOPs/W

- 2703 / 250 = 10.8 GFLOPs/W

#### Absolute hardware performance

- Only achieved in the optimal conditions:

- Processing units 100% used

- All parallelism 100% exploited

- All data transfers at maximum bandwidth

- In real life

- No application is like this

- Can we reason about "real" performance?

## HIGH-LEVEL OPERATIONAL VIEW

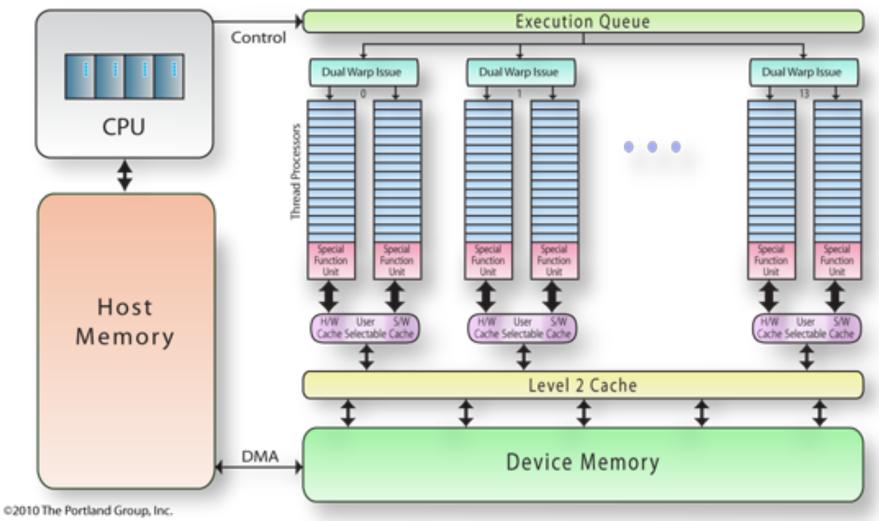

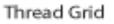

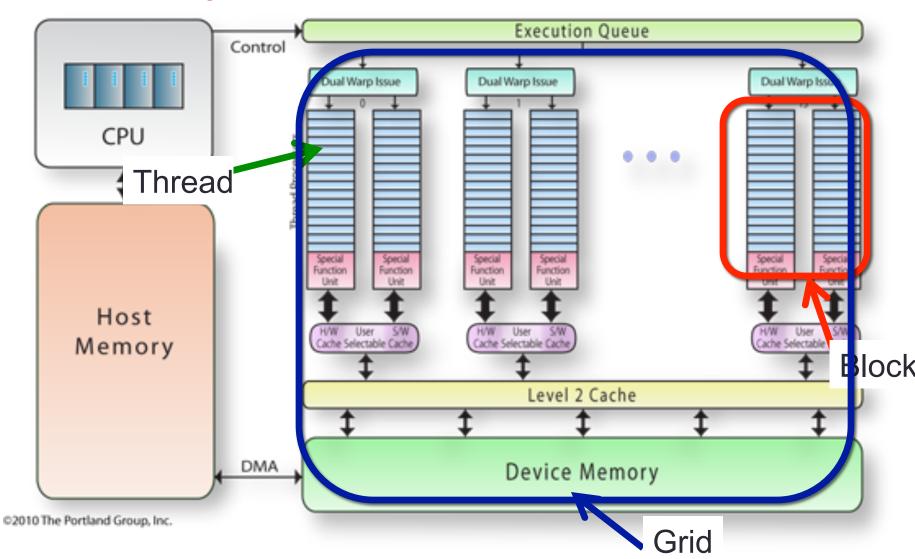

#### A GPU Architecture

#### Integration into host system

- Typically PCI Express 2.0

- Theoretical speed 8 GB/s

- Effective ≤ 6 GB/s

- In reality: 4 6 GB/s

- V3.0 recently available

- Double bandwidth

- Less protocol overhead

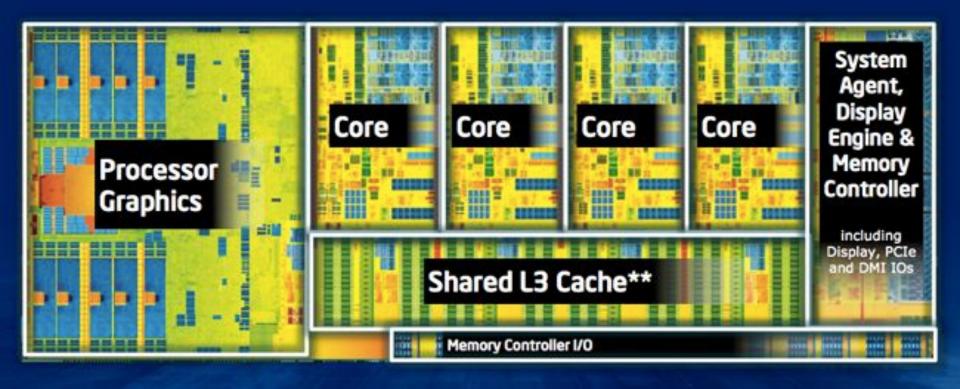

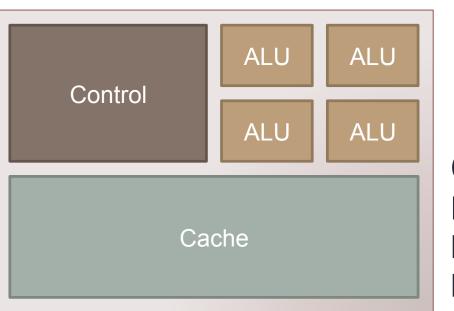

#### A CPU die

#### A GPU die: Fermi

### CPU vs. GPU

#### CPU

Few complex cores Lots of on-chip memory Lots of control logic

GPU many simple cores, little memory, little control

#### Why so different?

- Different goals produce different designs!

- CPU must be good at everything

- GPUs focus on massive parallelism

- · Less flexible, more specialized

- CPU: minimize latency experienced by 1 thread

- big on-chip caches

- sophisticated control logic

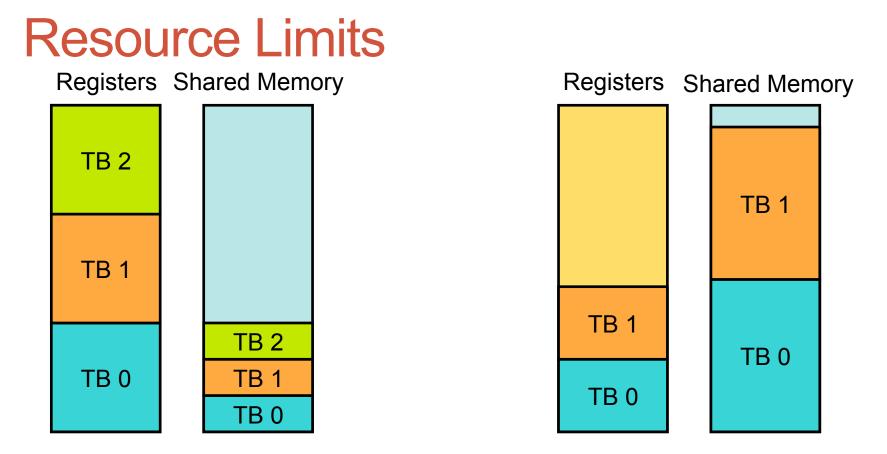

- GPU: maximize throughput of all threads

- # threads in flight limited by resources => lots of resources (registers, etc.)

- multithreading can hide latency => no big caches

- share control logic across many threads

#### CPU vs. GPU

- Movie

- The Mythbusters

- Jamie Hyneman & Adam Savage

- Discovery Channel

- Appearance at NVIDIA's NVISION 2008

## NVIDIA GPUS ARCHITECTURE

#### Fermi

- Consumer: GTX 480, 580

- HPC: Tesla C2050

- More memory, ECC

- 1.0 Tlop SP

- 515 GFlop SP

- 16 streaming multiprocessors (SM)

- GTX 580: 16

- GTX 480: 15

- C2050: 14

- SMs are independent

- 768 KB L2 cache

#### Fermi Streaming Multiprocessor (SM) SM Instruction Cache 32 cores per SM (512 cores total) Warp Scheduler Warp Scheduler **Dispatch Unit** Dispatch Unit 64KB configurable Register File (32,768 x 32-bit) L1 cache / shared memory LD/ST Core Core Core Core LD/ST SFU LD/ST • 32,768 32-bit registers Core Core Core Core LD/ST LD/ST Core Core Core Core LD/ST SFU LD/ST Host Interface Core Core Core LD/ST GigaThread Engin LD/ST Core Core Core Core LD/ST SFU LD/ST Core Core Core Core LD/ST ΠT ΠТ ╢┝╫╫┿ LD/ST TTT m Core Core Core Core ╶╌╌╣╒╌╌╣╒╌╌╣ LD/ST SFU LD/ST Core Core Core Core LD/ST Interconnect Network 64 KB Shared Memory / L1 Cache Uniform Cache Tex Tex Tex Tex mm HH Texture Cache ET THE ΠП PolyMorph Engine \_\_\_\_\_ TTTR Viewport Vertex Fetch Tessellator Transform Attribute Setup Stream Output

48

## Kepler: SMX

- Consumer:

- GTX680, GTX780, GTX-Titan

- HPC

- Tesla K10..K40, K80

- SMX features

- 192 CUDA cores

- 32 in Fermi

- 32 Special Function Units (SFU)

- 4 for Fermi

- 32 Load/Store units (LD/ST)

- 16 for Fermi

- 3x Perf/Watt improvement

- 4x more texture memory

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | Vertex I   | Fetch |      |         | Poly          | Morph<br>Tesse |        | 2.0  |        |         | iewport | Transf  | orm    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|-------|------|---------|---------------|----------------|--------|------|--------|---------|---------|---------|--------|-----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | - Sittex I |       | Attr | ibute S | etup          | 10550          |        | Stre | am Out |         | lewpon  | Tansi   | orm    |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      |         |               |                |        |      |        |         |         |         |        |     |

| V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /arp So | chedule    | er    |      | Varp S  | In:<br>chedul | structio<br>er | on Cac | _    | hedule | r       | v       | /arp So | hedule | r   |

| Dispatch Unit Di |         |            |       |      |         |               |                |        |      |        | Dispate |         |         |        |     |

| Register File (65,536 x 32-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      |         |               |                |        |      |        |         |         |         |        |     |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    |               | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| COLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    |            |       | Core |         |               |                |        |      |        |         | Core    |         |        |     |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    |         | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    |            | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core |        | Core    |         | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    |            | Core  | Core | Core    |               | SFU            | Core   | Core |        |         | Core    |         | LD/ST  | SFU |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      |         |               | н              |        |      |        |         |         |         |        |     |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

| Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core    | Core       | Core  | Core | Core    | LD/ST         | SFU            | Core   | Core | Core   | Core    | Core    | Core    | LD/ST  | SFU |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      |         |               | Texture        | Cache  |      |        |         |         |         |        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      | 64      |               | ared Me        |        |      | che    |         |         |         |        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |       |      |         |               | Uniform        |        | _    |        |         |         |         |        |     |

| Te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | Te         |       |      | вх      |               | ex             | Te     |      | Tex    |         | Tex     |         | Tex    |     |

| Te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | Te         | €X    | Ť    | ex      |               | ex             | Te     | X    | Te     | X       | Te      | ex 🛛    | Te     | X   |

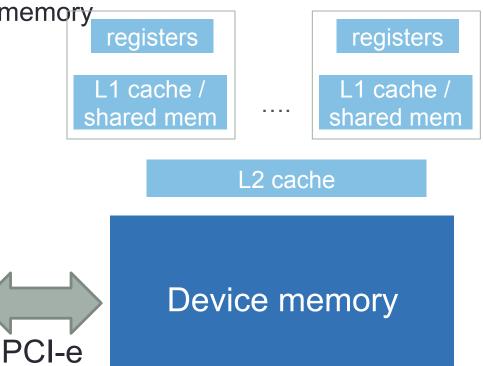

#### Memory architecture (since Fermi)

bus

- 16KB L1 cache / 48KB Shared memory

- 48KB L1 cache / 16KB Shared memory

Host memory

50

## Maxwell: SMM

- Consumer:

- GTX 970, GTX 980, ...

- HPC:

- Tesla M40

- SMM Features:

- 4 subblocks of 32 cores

- Dedicated L1/LM per 64 cores

- Dispatch/decode/registers per 32 cores

- L2 cache: 2MB (~3x vs. Kepler)

- 40 texture units

- Lower power consumption

|              |                    |                      |               | P                     |                                      | Engine 2.                                     | 0          |                 |             |                       |    |  |  |

|--------------|--------------------|----------------------|---------------|-----------------------|--------------------------------------|-----------------------------------------------|------------|-----------------|-------------|-----------------------|----|--|--|

|              | Verte              | x Fetch              | A 44-11       | ute Setup             | ellator                              | Stream O                                      | iewport T  | wport Transform |             |                       |    |  |  |

|              |                    |                      | Attrib        | ute Setup             |                                      |                                               | Stream O   | utput           |             |                       |    |  |  |

| _            |                    | _                    |               |                       | on Cache                             |                                               |            |                 | _           | _                     |    |  |  |

| _            | 1                  | nstructio<br>Warp So | on Buffe      | ŧ۲                    | Instruction Buffer<br>Warp Scheduler |                                               |            |                 |             |                       |    |  |  |

| Di           | spatch Uni         | t                    | D             | lispatch Ur           | D                                    | ispatch Uni                                   | it         |                 | lispatch Ur | nit                   |    |  |  |

|              |                    | er File (1           | 16,384 x      |                       |                                      |                                               | er File (1 | 16,384 x        |             |                       |    |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

| Core         | Core               | Core                 | Core          | LD/ST                 | SFU                                  | Core                                          | Core       | Core            | Core        | LD/ST                 | SF |  |  |

|              | Texture / L1 Cache |                      |               |                       |                                      |                                               |            |                 |             |                       |    |  |  |

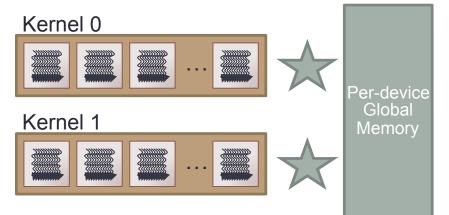

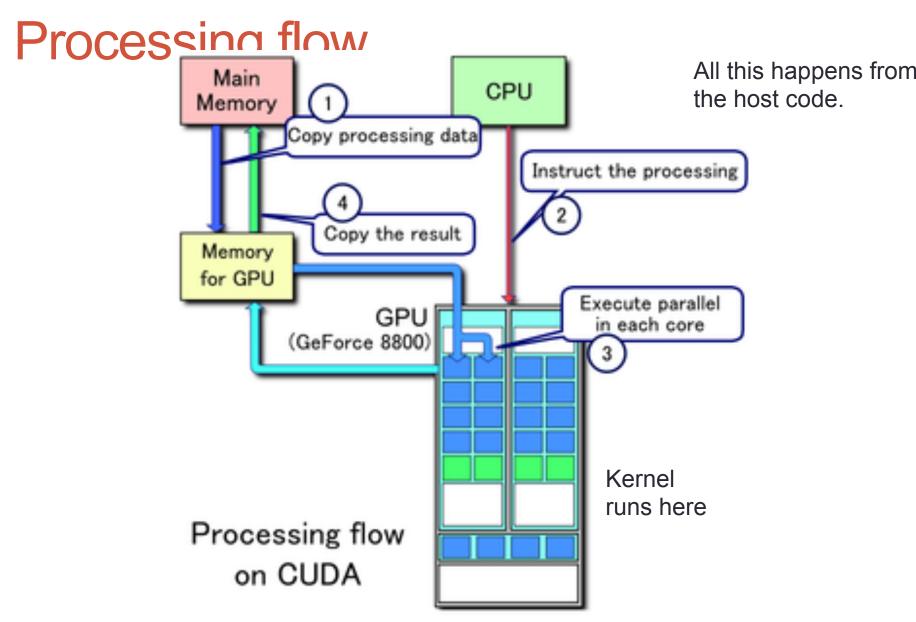

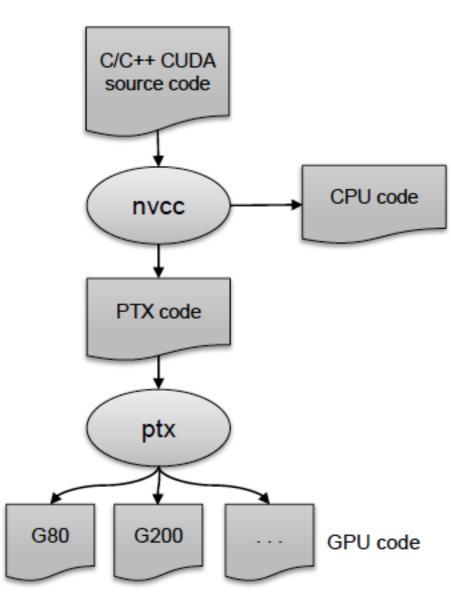

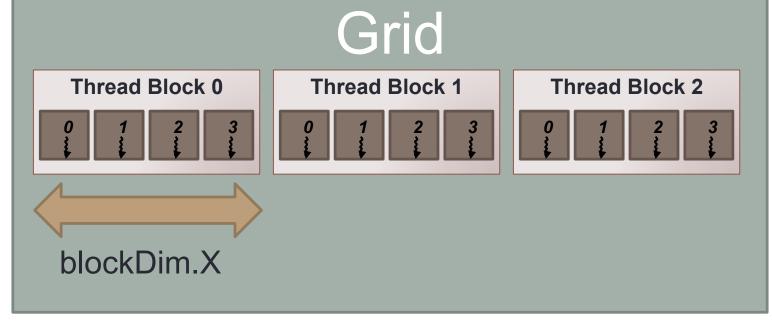

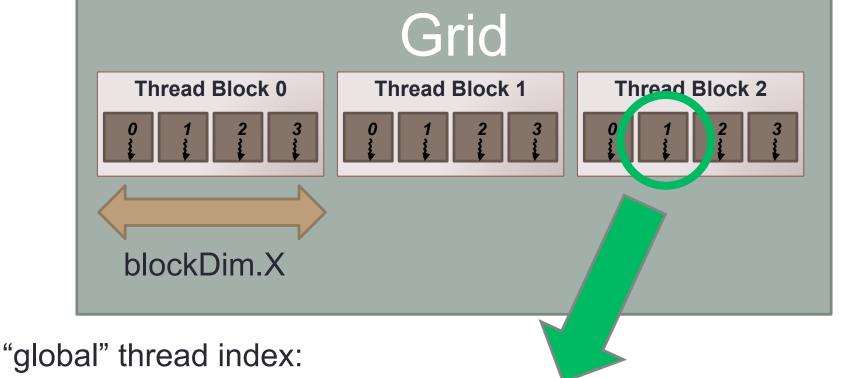

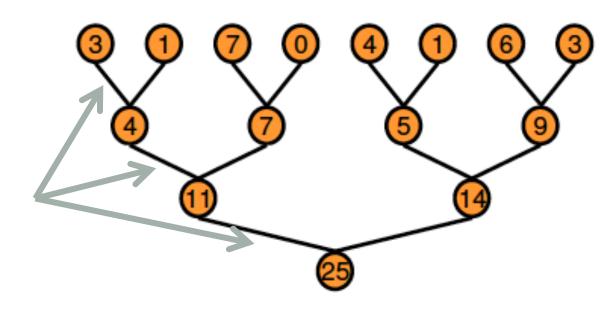

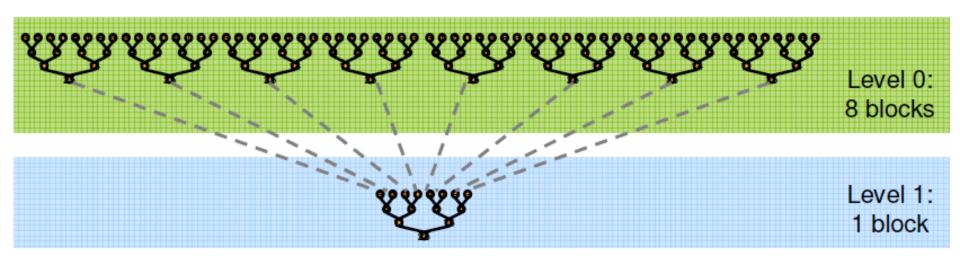

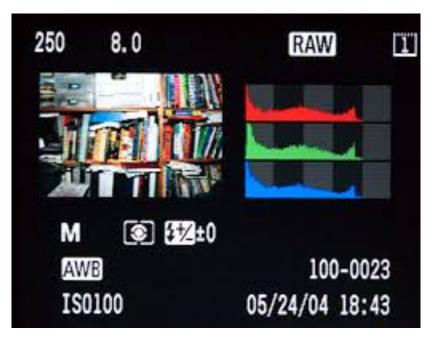

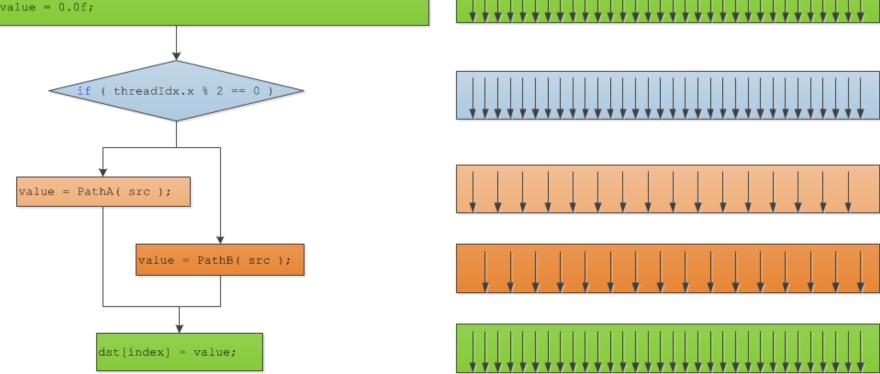

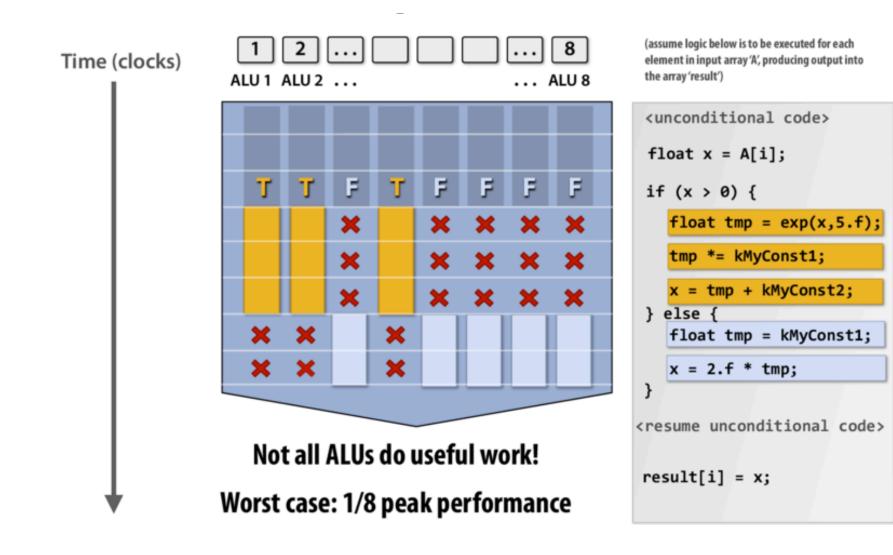

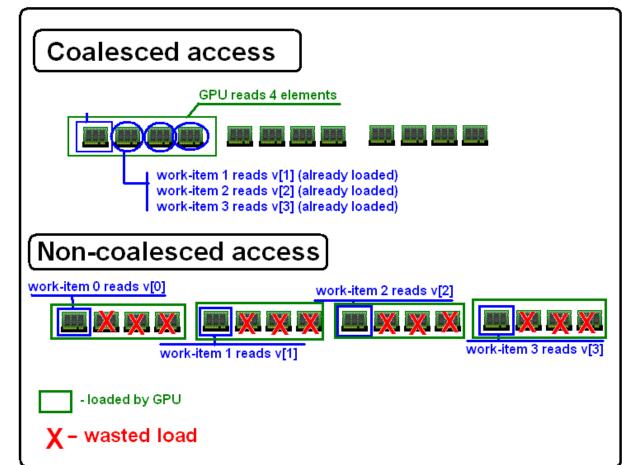

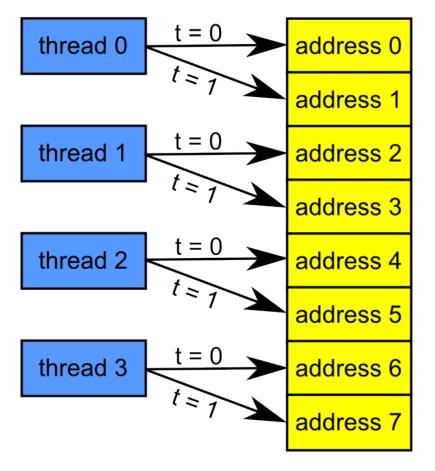

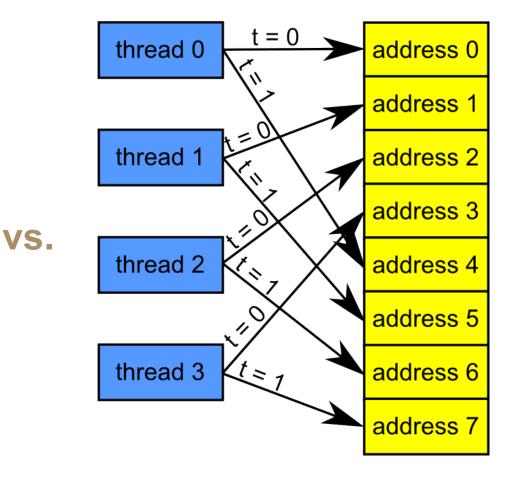

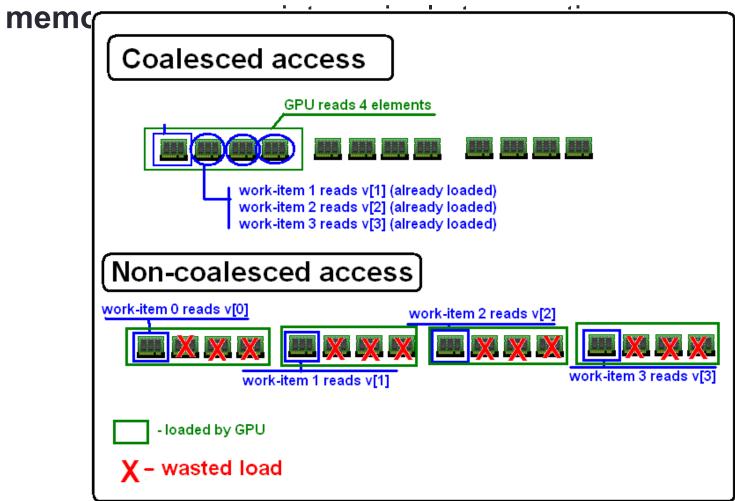

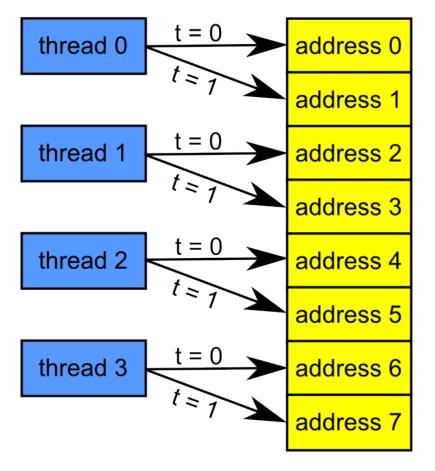

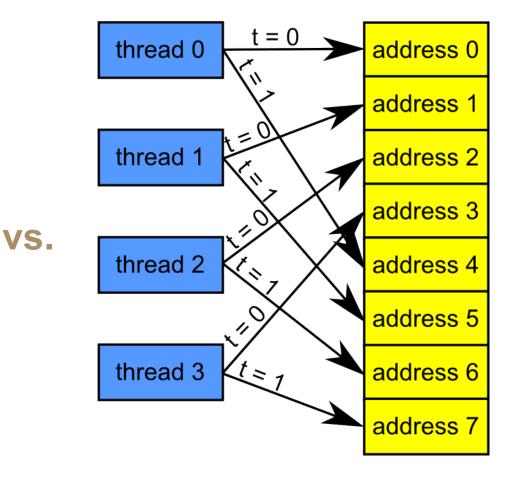

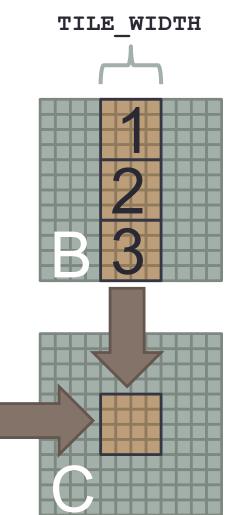

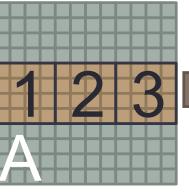

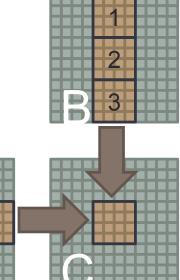

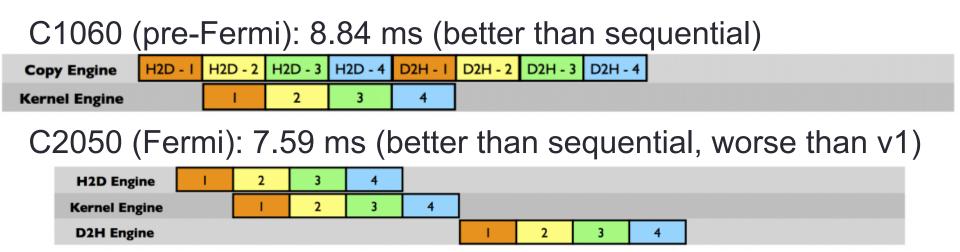

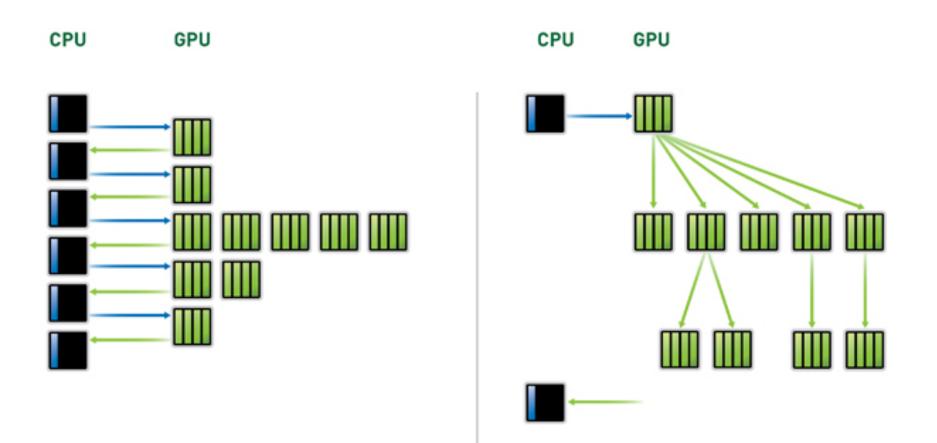

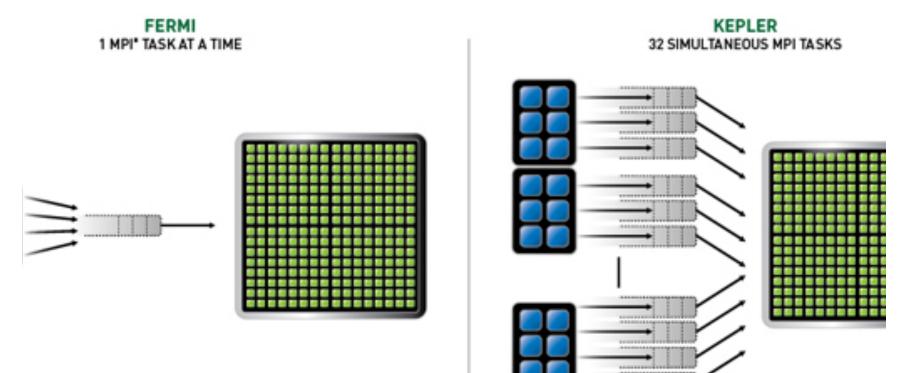

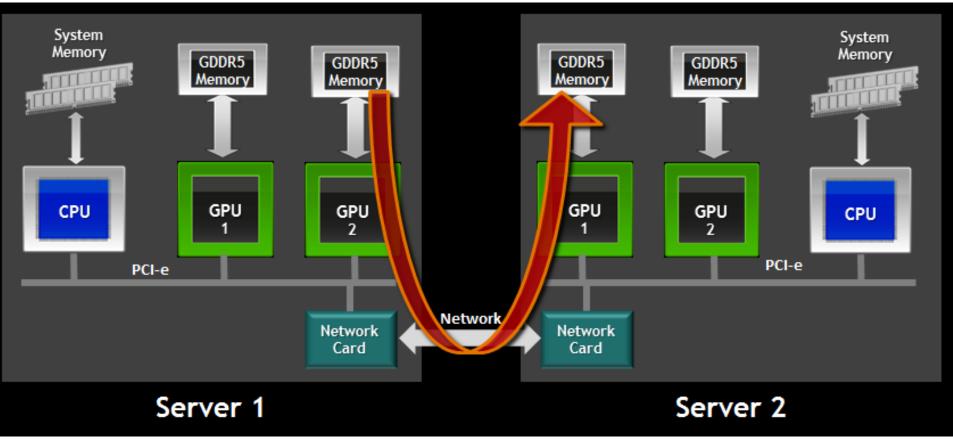

|              | Tex                |                      |               | Tex                   |                                      | Tex Tex                                       |            |                 |             |                       |    |  |  |